74HC109D,652

Ознакомьтесь c описанием продукта. Сообщить об ошибке.

- 1597+ 48.07

Добавить в корзину 1597 шт. на сумму 48.07 ₽

74HC109D,652 характеристики

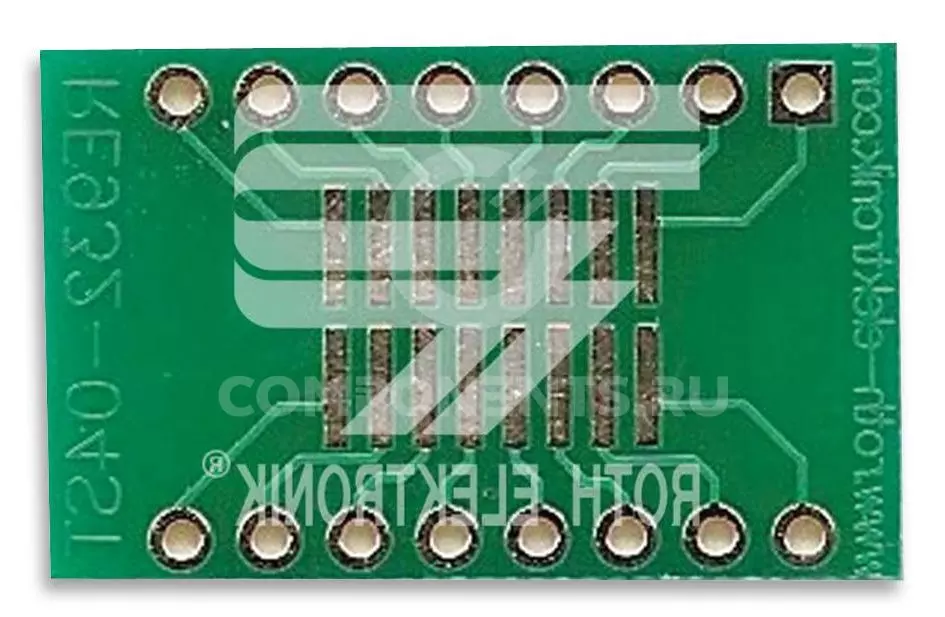

Триггер, дополнительный выход, положительный фронт, JK, 75 МГц, SOIC, 16 вывод(-ов).

The 74HC109D is a positive-edge trigger Dual J K\ Flip-flop with set and reset. This high-speed Si-gate CMOS device is pin compatible with low power Schottky TTL (LSTTL). It is specified in compliance with JEDEC standard no. 7A. The dual positive-edge triggered J K\ flip-flops with individual J, K\ inputs, clock (CP) inputs, set (SD\) and reset (RD\) inputs, also complementary Q and Q\ outputs. The set and reset are asynchronous active LOW inputs and operate independently of the clock input. The J and K\ inputs control the state changes of the flip-flops as described in the mode select function table. The J and K\ inputs must be stable one set-up time prior to the low-to-high clock transition for predictable operation. The J K\ design allows operation as a D-type flip-flop by tying the J and K\ inputs together. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

Техническое описание

74HC109D,652 скачать

Pdf, 7.4 KB

74HC109D,652 скачать

Pdf, 7.4 KB

Вы можете купить 74HC109D,652 от 1 штуки. Работаем с частными лицами и с юридическими лицами по безналичному расчету.

Доступно на складе 55250 штук. Цена 74HC109D,652 зависит от объёма заказа, минимальная стоимость составляет 18026.25 руб.