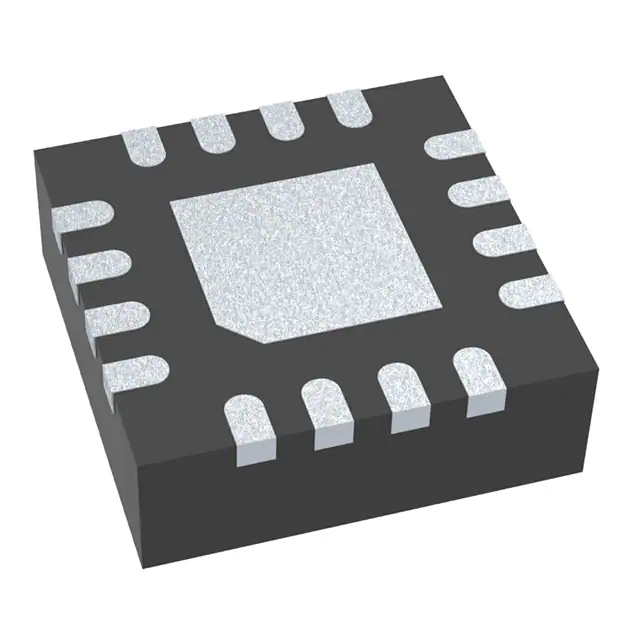

CDCLVP1102RGTT

Ознакомьтесь c описанием продукта. Сообщить об ошибке и получить баллы.

- 1+ 1517.67

- 10+ 1167.24

- 25+ 1079.6

- 75+ 924

Добавить в корзину 1 шт. на сумму 1517.67 ₽

CDCLVP1102RGTT характеристики

CLK, BUFF, 1:2, LVPECL, SGL, 16QFN.

The CDCLVP1102RGTT is a highly versatile low additive Jitter Buffer can generate two copies of LVPECL clock outputs from one LVPECL, LVDS or LVCMOS input for a variety of communication applications. It has a maximum clock frequency up to 2GHz. The overall additive jitter performance is less than 0.1ps, RMS from 10kHz to 20MHz and overall output skew is as low as 10ps, making the device a perfect choice for use in demanding applications. The CDCLVP1102 clock buffer distributes a single clock input (IN) to two pairs of differential LVPECL clock outputs (OUT0, OUT1) with minimum skew for clock distribution. The inputs can be LVPECL, LVDS or LVCMOS/LVTTL. The CDCLVP1102 is specifically designed for driving 50R transmission lines. When driving the inputs in single-ended mode, the LVPECL bias voltage (VAC_REF) should be applied to the unused negative input pin. However, for high-speed performance up to 2GHz, differential mode is strongly recommended.

Техническое описание

CDCLVP1102RGTT скачать

Pdf, 7.07 KB

CDCLVP1102RGTT скачать

Pdf, 7.07 KB

Вы можете купить CDCLVP1102RGTT от 1 штуки. Работаем с частными лицами и с юридическими лицами по безналичному расчету.

Доступно на складе 509 штук. Цена CDCLVP1102RGTT зависит от объёма заказа, минимальная стоимость составляет 924 руб.