Стандартом чиплетов становится 3D

Стандарты, определяющие технологии чиплетов, переживают второе воплощение.

Созданный в марте 2022 года консорциум Universal Chiplet Interconnect Express (UCIe) недавно выпустил спецификацию 2.0 с обновлениями, касающимися проектирования в части тестируемости, управляемости и отладки (DFx) SiP на нескольких чиплетах в течение их жизненного цикла. Ключевой особенностью обновления является поддержка 3D-упаковки, что позволит чиплетам значительно увеличить плотность полосы пропускания и энергоэффективность.

Председатель консорциума Дебендра Дас Шарма заявил на брифинге, что спецификация UCIe 2.0 является полностью обратно совместимой, представляя дополнительные функции управления и архитектуру UCIe DFx (UDA), что обеспечивает поддержку взаимодействие чиплетов вне зависимости от производителя.

Консорциум разделил работу над спецификацией между несколькими рабочими группами, сосредоточившимися на разных аспектах: электрика, протокол, форм-фактор и соответствие, управляемость и безопасность, а также системы и программное обеспечение. Дас Шарма сказал, что недавно сформированная группа по автомобильной промышленности отражает интерес этой отрасли к тому, чтобы начать определять свои запросы.

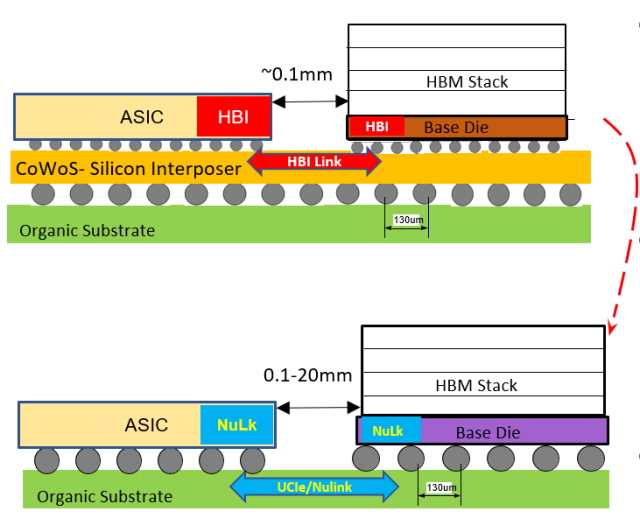

Он называет UCIe 1.0 «плоским соединением», так как оно поддерживает 2D и 2.5D, что означает, что чиплеты располагаются бок о бок. Новая спецификация поддерживает вертикальную 3D-укладку чиплетов, обеспечивая необходимую взаимосвязь между ними.

Другое ключевое обновление в UCIe 2.0, сказал Дас Шарма, касается управляемости, включая отладку и тестирование как на пластине, так и после упаковки чиплетов. Другой новой функцией в 2.0 являются оптимизация пакетного дизайна для тестирования взаимодействия и совместимости.

Среди поддерживаемых в UCIe 2.0 механизмов управляемости также присутствует обнаружение чиплетов и их конфигурация, управление питанием и температурой, отчеты об ошибках, а также различные аспекты безопасности чиплетов. По словам Дас Шармы, что эти механизмы используют подходящие отраслевые стандарты вне зависимости от основных протоколов самих чиплетов. Также подобные механизмы предназначены для работы с чиплетами от разных производителей и поддерживают их специфичные расширения.

Возможности UCIe-3D в спецификации UCIe 2.0 оптимизированы для гибридного соединения, чтобы обеспечить гибкость и масштабируемость. (Источник: Консорциум UCIe)

Он добавил, что одним из направления в 3D для чиплетов является переход к гибридному соединению, которое становится все более распространенным и позволяет существенно уменьшить шаг микровыступов между чипами. 3D-соединение почти полностью убирает расстояние между чиплетами, следовательно, совместимость будет ограничена именно шагом микровыступов.

Спецификация UCIe-3D оптимизирована для гибридных соединений посредством с микровыступов с шагом от 10-25 микрон до одного микрона и менее, что обеспечивает гибкость и масштабируемость.

Дас Шарма сказал, что малый размер соединений подразумевает энергоэффективность. «Мощность становится значительно ниже, так как не наблюдается помех даже внутри чиплета», — сказал он. «Это очень простая схема».

UCIe идёт по стопам наиболее развитых технологий межсоединения, таких, как PCI Express и Ethernet, с целью удвоения плотности полосы пропускания, в то же время оптимизируя энергоэффективность, говорит Дас Шарма.

В области безопасности UCIe 2.0 использует хабовую («звездообразную») модель, добавил он, где управляющий директор выступает в качестве «корня доверия» (Root-of-Trust). «Мы усиливаем безопасность на уровне пакета».

Технология чиплетов не нова, но лишь в последние годы пришло понимание необходимости улучшить методы, стандарты и инструменты при её внедрении. В конце 2022 года вышел из тени стартап из Кремниевой долины Eliyan Corporation, предложив более эффективный подход к упаковке. Их система «пучок проводов» (BoW) нацелена на достижение таких же, как и у интерфейса «от кристалла к кристаллу» (D2D), пропускной способности, энергоэффективности и задержки, применяя передовые технологий при стандартном методе упаковки.

Система чиплетов BoW от стартапа Eliyan из Кремниевой долины нацелена на достижение той же пропускной способности, энергоэффективности и задержки, что и при реализации «от кристалла к кристаллу». (Источник: Eliyan)

Совсем недавно, в июне 2024 года, дал о себе знать ещё один стартап, чья деятельность направлена на упрощение разработки систем чиплетов. WeaverPro, платформа архитектуры для управляемых алгоритмами систем от Baya Systems, сочетая масштабируемую IP и кэш-структуру Weave IP, объединяет все шаги создания чиплетов посредством проектирования и оптимизации на основе данных, чтобы ускорить анализ, проектирование и внедрение чиплетов.

Дас Шарма сказал, что UCIe 2.0 будет стремиться к обратной совместимости с версией 1.0 в плане соответствия наиболее «зрелым» протоколами межсоединений, PCIe и NVMe.

Но хотя протоколы взаимодействия и установили трехлетний цикл обновлений (даже CXL, вероятно, будет следовать этой схеме после тройного обновления за небольшой период), Дас Шарма заявил, что неясно, как стабилизируется UCIe.

По его словам, многочисленным группам, работающим над новой версией, предстоит немало сделать. «В данный момент хватает действительно интересных моделей и задач, которые нам нужно решить».

Оригинальные электронные компоненты